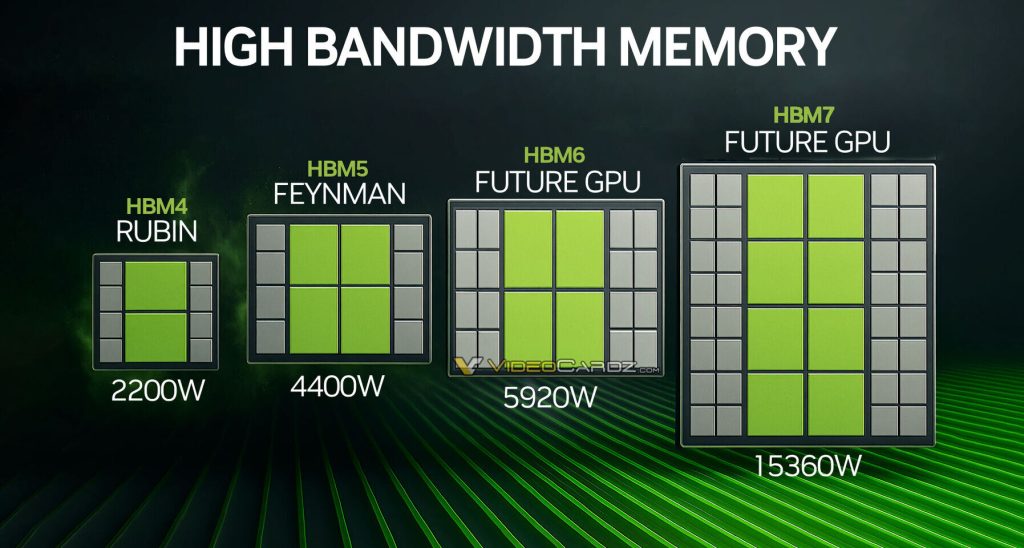

在本周的联合简报会上,韩国科学技术研究院(KAIST)内存系统实验室和 TERA 互连与封装团队展示了高带宽内存 (HBM) 标准及其加速器平台的前瞻性路线图。该路线图涵盖了从 HBM4 到 HBM8 的五代产品,每代产品都有望在容量、带宽和封装复杂度方面实现大幅提升。 首先是 HBM4,计划于 2026 年在 AI GPU 和数据中心加速器中推出。它将通过 2048 位接口以 8 Gbps 的引脚速率提供每堆栈约 2 TB/s 的数据传输率。芯片堆栈将达到 12 至 16 层,每个封装可提供 36-48 GB 的…