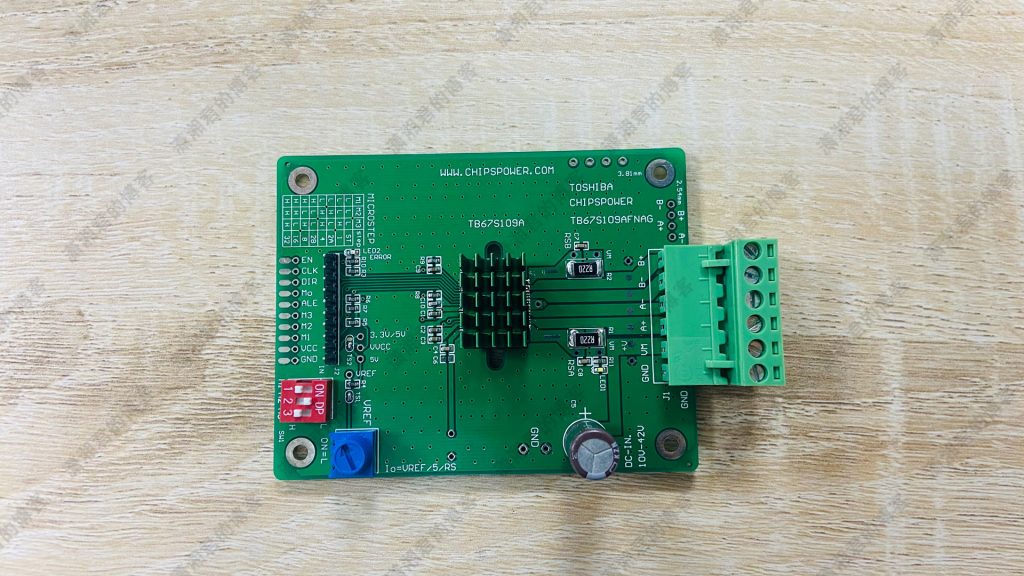

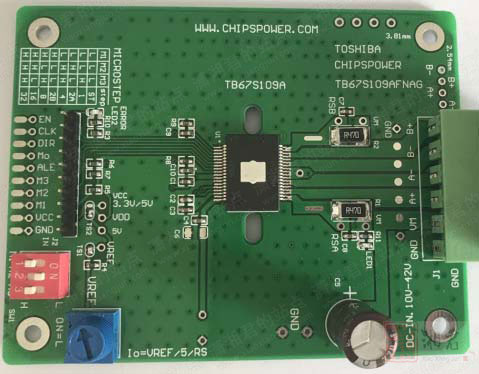

TB67S109AFNAG-IO是我司基于一款东芝 TB67S109AFNAG 步进电机芯片所制作的测试板,以下是它的测试说明。

使用说明

图示中 SW1设置细分,电位器调整输出电流,LED1电源指示灯,LED2报警指示灯.

逻辑控制信号:高电平大于2V,低电平小于0.8V。具体请参考芯片文档。

信号输入端

GND :信号地输入端

VCC: 信号电源输入端(TS2用于选择部分控制信号的电源,默认连接的是板内5V)

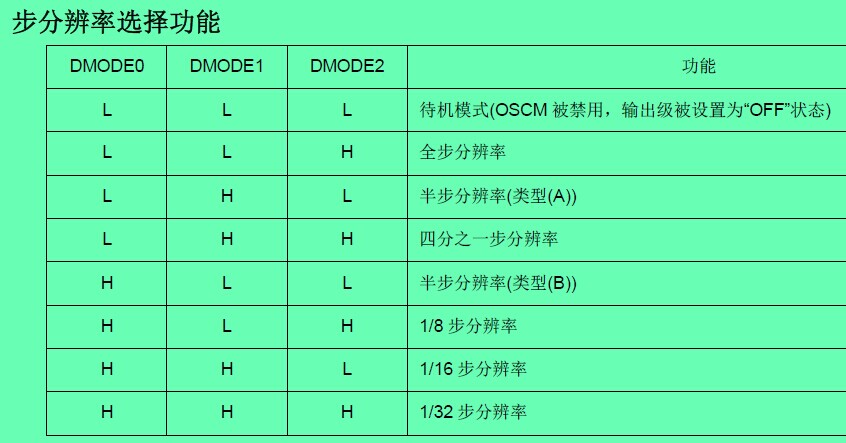

M1: 励磁模式设置输入端(细分设置端DMODE0)

M2: 励磁模式设置输入端(细分设置端DMODE1)

M3: 励磁模式设置输入端(细分设置端DMODE2)

ALE:报警输出端。(对应芯片的ALERT引脚,当芯片进入保护状态会拉低ALE)

Mo: 电角监视引脚。(对应每4个整步,Mo拉低一次)

DIR: 步进方向信号输入端。(对应芯片的CW/CCW引脚)

CLK:步进脉冲信号输入端。(一个脉冲走一步,脉冲的频率决定步进电机的速度)

EN: 使能信号输入端。(对应芯片的ENABLE引脚,低电平时关闭芯片的功率输出)

电机绕组连接: (注意RS的值,板是用2个0.47欧的并联,这样最大电流在3A以内。若要更大的电流,请更换RS)

(1)A+:连接电机绕组A相。

(2)A-:连接电机绕组A相

(3)B+:连接电机绕组B相。

(4)B-:连接电机绕组B相。

步进电机绕组并无正负之分,接入驱动时注意区分绕组。另外,要改变电机的初始启动方向时,调换其中一个绕组的接线。比如把A+与A-的接线交换,即使改变电机的初始启动方向。

工作电压的连接:

(1)VM: 连接直流电源正。(推荐工作电压范围9~42V)

(2)GND:连接直流电源负。

电流设置(电流值)

可通过该电流检测电阻(RS)与基准电压(Vref),设置峰值输出电流(设置当前值),如以下所述:

Iout(最大值) = Vref / 5 / RS

平均电流小于计算值,原因是该IC 采用峰值电流检测法。所以不要用电源端检测的电流值与设置的电流值比较。

芯片的VCC端是内部稳压端引出,用于外接滤波电容(0.1uF~1uF)。外部电路要用芯片的VCC供电时,建议VCC的输出电流不要超过5mA。如果外部有5V稳压电源,原则上不建议与芯片的VCC端直接连接。因为两个稳压电路输出有压差时,可能会有影响。不管芯片外围线路是否用内部VCC供电,芯片的VCC端都必须加上滤波小电容.

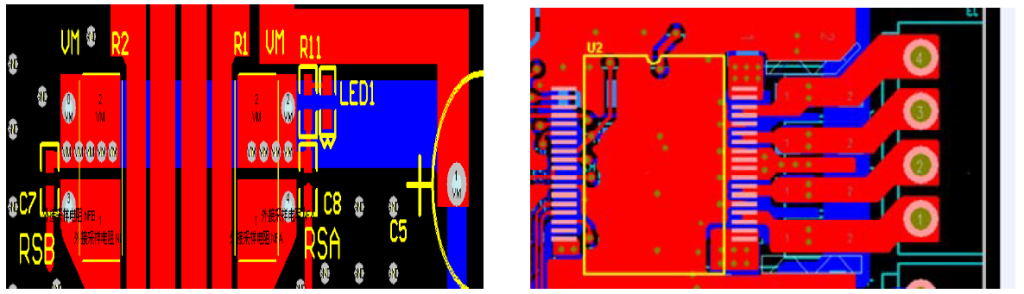

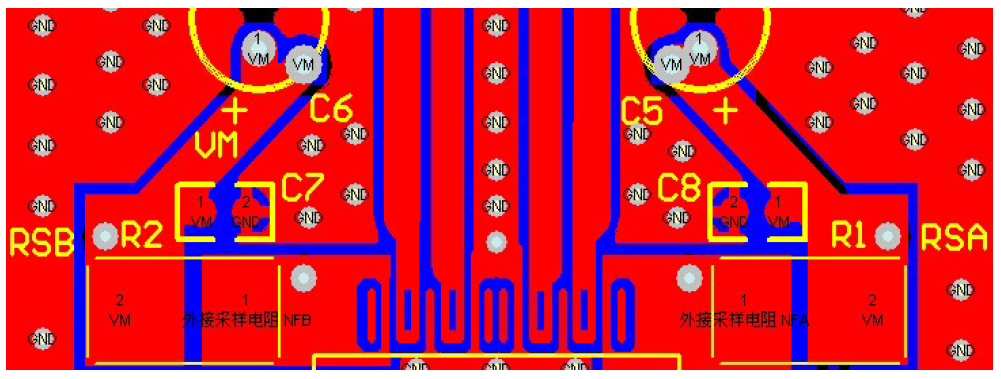

关于PCB设计方面,要注意处理好大电路线路。像NFA(RSA采样电阻网络)、NFB(RSB采样电阻网络)、A+、A-、B+、B-这些都是大电流线路,如果需要层间切换布线的,在放置过孔时建议要多放几个,以降低布线带来的阻抗。另外,如果应用中对电机的锁相噪音有要求,要注意处理采样电阻两端的连线。测试确认,采样电阻任意一端的连线,单纯通过过孔实现层间切换走线,可以明显降低锁相噪音。芯片23、26、29、32这几个GND引脚属于功率地,要注意处理。

能降低锁相噪音的两种PCB处理方式,关注点是RS电阻两端的连线:

关于步进电机的速度方面,在空载启动速度大于60转时,建议做加减速控制,以免避启动堵转或者丢步。带载的则要具体测试。加减速控制,可以避免突然启动、停止对电机和驱动部分的冲击,同时也可以带来很好的驱动效果。比如缓启、缓停。具体的可以网络搜索一下相关文档来参考。

拓展应用

拓展应用电路,在应用中根据需要增加功能.

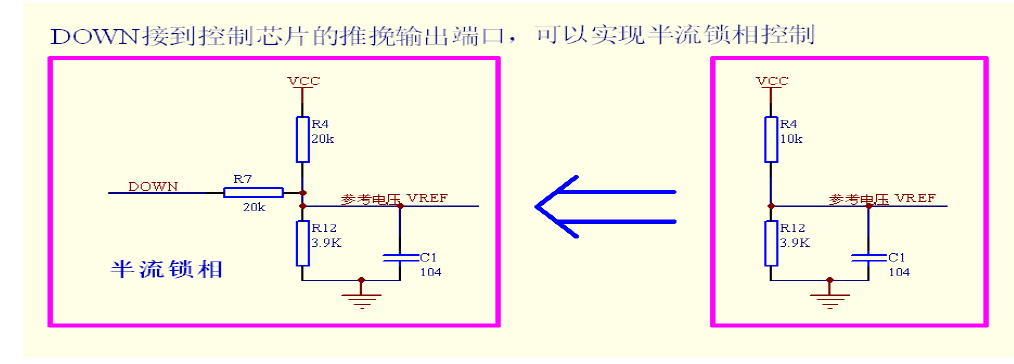

用来实现降低锁相电路,从而降低驱动芯片的锁相功耗,具体应用电路如下图:

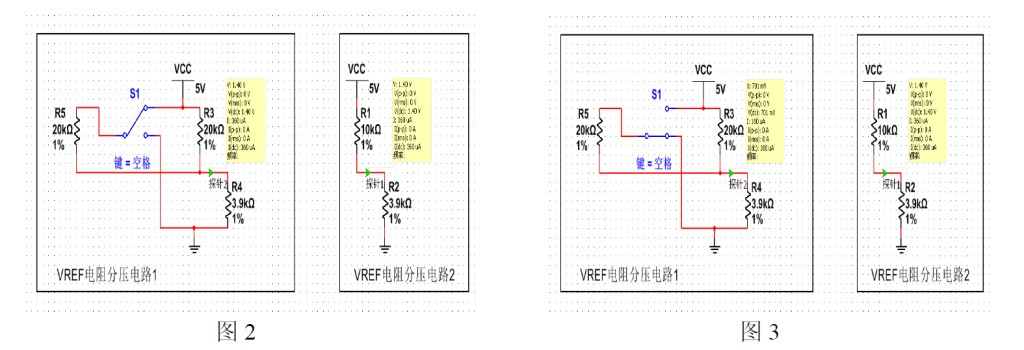

图1,左、右两方框电路用来设置参考电压。当VCC=5V,DOWN≈VCC,两方框生成的分压值相等。 当DOWN=L(≈GND),参考电压会降低一半。具体看下面仿真图中的数据差异:

图2、图3中的S1可以用推挽输出端口代替,比如74LVC245、MCU等等,只要高电平与VCC大约相等。 这样就可以通过其它器件来实现半流锁相。注:推挽端口输出状态只有高电平、低电平两种。若是端口是开路输出的,相应要调整电阻参数。

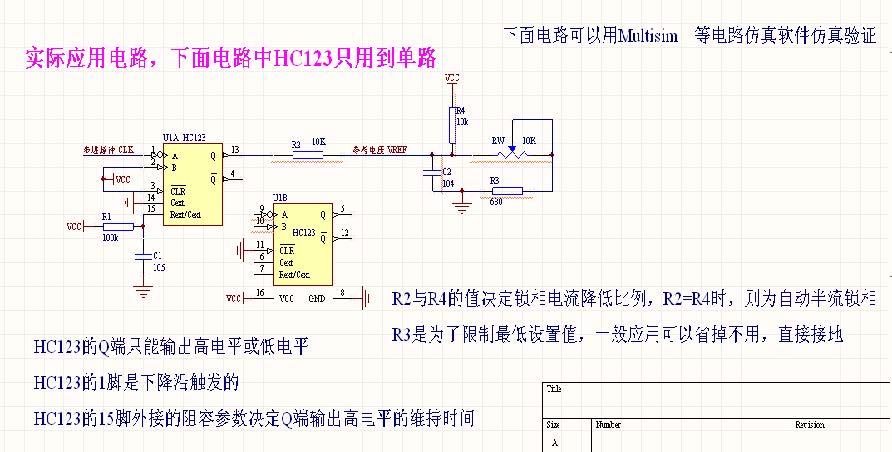

使用74HC123实现的自动半流锁相电路

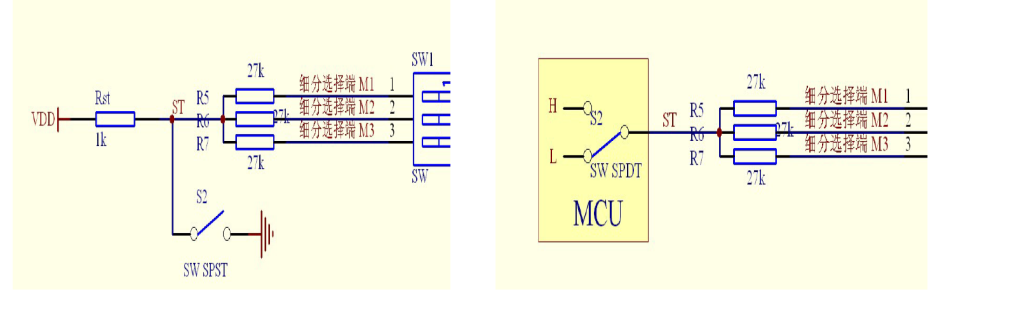

待机功能的单端口控制(ST的作用1是实现待机控制。作用2是让芯片从保护状态中恢复正常工作)

芯片的待机(ST)功能整合在细分表中,只能通过细分设置端来选择ST功能。

上面是两种简化实现单端口控制ST的电路

文章评论