PCI-SIG 正式发表 PCIe 7.0 标准,新增光纤应用设计范畴,并宣布开始研发 PCIe 8.0。

先前释出多个修订版本之后,PCI-SIG终于宣布推出PCIe 7.0正式规范,标榜能以128.0 GT/s传输规格满足当前人工智慧运算的频宽需求。此外,PCI-SIG更宣布在PCIe 6.4及PCIe 7.0设计规范纳入光纤应用,藉此对应更高数据传输表现,同时也让光纤应用成为设计标准。

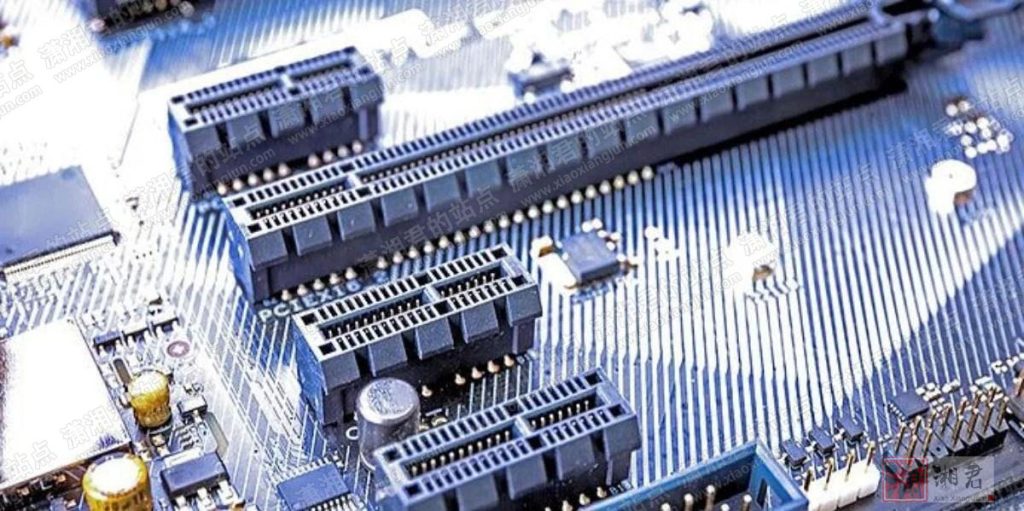

PCIe 7.0设计可对应最高高达512 GB/s的双向传输速率表现

在此次成为正式规范的PCIe 7.0设计中,标榜其数据传输速率可达128.0 GT/s,更可在x16配置下实现高达512 GB/s的双向传输速率,主要因应人工智慧/机器学习、800G乙太网路、云端运算及日后预期普及的量子运算作准备。

此外,PCIe 7.0设计也採用PAM4 (四级脉衝幅度调变)讯号和基于Flit (流量控制单元)的编码设计,藉此进一步提高能源使用效率,并且确保与前面几代的PCIe设计规格相容。

PCI-SIG总裁暨主席Al Yanes表示,随著人工智慧应用持续快速扩展,下一代PCIe技术将满足佈署人工智慧的数据密集型市场频宽需求,包括超大规模数据中心、高性能计算 (HPC)、汽车,以及军事/航空航天等应用场景。同时,市场分析业者More Than Moore的首席分析师暨执行长Ian Cutress也指出,目前多数资料中心已经做好佈署基于PCIe 7.0技术的网路架构相关准备。

光纤应用成为PCIe 6.4与PCIe 7.0设计规范标准之一

而PCI-SIG也宣布新版光互连规范修订,并且加入PCIe 6.4与PCIe 7.0设计规范,其中新增基于PCIe重定时器 (retimer)的设计,藉此让光纤应用能成为PCIe技术标准化规格。

在此标准之下,将使PCIe 6.4与PCIe 7.0设计规范无缝支援各种光连接技术,实现现有符合PCIe 6.4及PCIe 7.0规范设计交换器、根複合体 (root complex)装置与端点晶片设计之间的光互连需求,同时也能藉由光连接技术扩充跨机架及pod组合的连接范围,同时也加入跨电域及光域进行多路複用、资料映射使用需求,同时也能实现比铜缆线设计更为紧凑的晶片设计方案。

文章评论